智东西12月15日消息,近日在IEEE电子器件会议(IEDM)上,台积电、加州大学圣地亚哥分校、斯坦福大学的工程师介绍了一种新的制造工艺,能够更好地控制碳纳米晶体管沉积高K电介质,这种控制对于确保晶体管在需要时完全关闭至关重要。

简单地说,该研究团队发明了一种制造栅极电介质的新工艺。栅极电介质是一种在栅电极和晶体管沟道区之间的绝缘层,在工作时,栅极处的电压会在沟道区中形成电场,从而切断电流。

近年来,人们对碳纳米晶体管的兴趣越来越高,主要原因在于它们有可能做到比硅晶体管缩得更小,并提供了一种比硅晶体管更容易制造出多层电路的方法。得益于一系列发展,如今的碳纳米管也逐渐接近硅的功能。

但几十年来,随着硅晶体管尺寸逐渐缩小,由二氧化硅制成的绝缘层必须变得越来越薄,以便用更少的电压来控制电流,从而降低能耗。最终,绝缘屏障变得非常薄,薄到电荷都可以穿过它,从而导致电流泄漏、浪费能量。

因此,如何解决晶体管的漏电和能量浪费等问题,也是行业一直研究的重要方向。

一、以往的二氧化铪新介电材料仍存在问题

十多年前,硅半导体行业通过改用一种新的介电材料——二氧化铪(hafnium dioxide,HfO2)解决了这一问题。

与二氧化硅相比,二氧化铪具有较高的介电常数(High-K),意味着一个相对较厚的高K电介层在电气上等效于一个非常薄的氧化硅层。

尽管研究人员们希望在碳纳米管晶体管中使用二氧化铪来形成栅极电介质,但碳纳米管有一个问题是——它们无法在按比例缩小的设备所需薄层中形成高K电介质。

高K电介质如何形成?它的沉积方法称为原子层沉积。顾名思义,它是一种在硅的表面自然形成的氧化层,像原子一样薄。但它一次只能构建一个原子层,并需要一个能够形成沉积的“基座”。

但由于二氧化碳和一氧化碳都属于气体,碳纳米管并没有能形成沉积的“立足点”,无法自然形成氧化层。同时,纳米管中任何可能导致所需“悬挂键”的缺陷都会限制其传导电流的能力。

悬挂键是一种化学键,一般晶体因晶格在表面处突然终止,在表面的最外层的每个原子将有一个未配对的电子,即有一个未饱和的键,这个键称为悬挂键。

▲纳米管(中心微弱的圆)和晶体管栅极(顶部的黑色部分)

二、形成高K电介质新解法:二氧化铪与氧化铝结合

“形成高K电介质一直是一个大问题。”台积电首席科学家、斯坦福大学教授黄汉森谈到,必须基本上将比纳米管更厚的氧化物倾倒在纳米管顶部,而不是倒在缩小的晶体管中。

他认为,如果要弄清楚为什么会出现这个问题,可以把栅极电压的作用想象成用脚踩在花园的水管上,尝试阻止水从水管中流过,但如果在脚和水管之间放一堆枕头(类似一个厚的氧化物),想要阻止水流经过就会变得更加困难。

台积电的Matthias Passlack和加州大学圣地亚哥分校的Andrew Kummel教授提出了一个解决方案,就是将二氧化铪的原子层沉积与沉积中间的介电常数材料氧化铝(Al2O3)结合起来。

氧化铝是使用加州大学圣地亚哥分校发明的纳米雾工艺沉积的。像水蒸气凝结形成雾一样,氧化铝凝结成簇覆盖在纳米管表面,以便二氧化铪可以将表面的电介质作为立足点,开始进行原子层沉积。

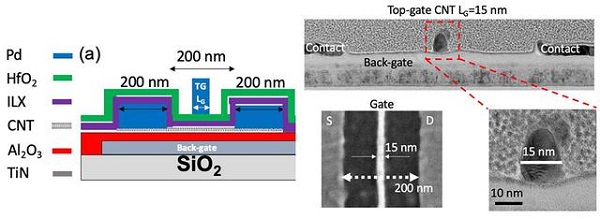

这两种介质的综合电学特性使该团队能够在只有15nm宽的栅极下,制造出厚度小于4nm的栅极电介质,最终得到的器件与硅CMOS器件具有相似的I/O电流比特性。同时仿真表明,即使是具有更薄栅极电介质的小器件也能正常工作。

三、碳纳米管超越硅晶体管仍有一定距离

但在碳纳米管器件能够与硅晶体管相媲美之前,还有很多工作需要完成。目前,尽管一些问题已得到解决,但尚未整合到单个设备中。

例如,黄汉森提出的设备中单个纳米管限制了晶体管可以驱动的电流。他也提到,要让多个相同的纳米管完美对齐一直是个挑战。

但在近期,北京大学彭连茂教授的实验室研究人员成功通过技术让每微米排列了250个碳纳米管,这意味着相应的解决方案可能很快就会出现。

另一个问题是设备的金属电极和碳纳米管之间的电阻,特别是当这些触点的尺寸缩小接近至当下先进硅芯片使用的尺寸时。

去年,黄汉森教授的学生Greg Pitner(现为台积电研究员及IEDM研究的主要作者)报告了一种方法,可以将一种接触类型(P型)的电阻降低到只有10nm接触理论极限的两倍以内。

但碳纳米管的N型触点还未达到类似的性能水平,同时CMOS逻辑芯片也包含两种类型。

还有一个问题是需要掺杂碳纳米管以增加栅极两边的载流子数量,主要在硅中通过用其他元素替换晶格中的一些原子来实现。

但这在碳纳米管中是行不通的,因为这会破坏结构的电子能力。相反,碳纳米管晶体管使用的是静电掺杂。在这种情况下,介电层的成本会被有意地操纵,以将电子抽出来或为纳米管提供电子。

黄汉森提到,他以前的学生Rebecca Park在该层中使用氧化钼取得了很好效果。

结语:半导体晶体管创新任重道远

随着近年来摩尔定律逐渐放缓,行业也一直尝试从材料、封装、工艺等不同方向来探索晶体管进一步创新发展的可能性。

但目前看来,尽管每个研究方向都有了一定的进展,但它们的可行性离真正落地还有较远的距离。如何将这些创新成果更好地结合在一起,以开发出超越硅的技术,研究人员们想要实现的这一未来仍任重道远。

(来源:智东西)